# 第8章 S3C44B0X 概述

# 第8章 目录

- □1.S3C44B0简介

- □2.存储器配置

- □3.时钟和功耗管理

- □4.CUP Wrapper和总线 特性

# 第8章 目录

- □1.S3C44B0简介

- □2.存储器配置

- □3.时钟和功耗管理

- □4.CUP Wrapper和总线 特性

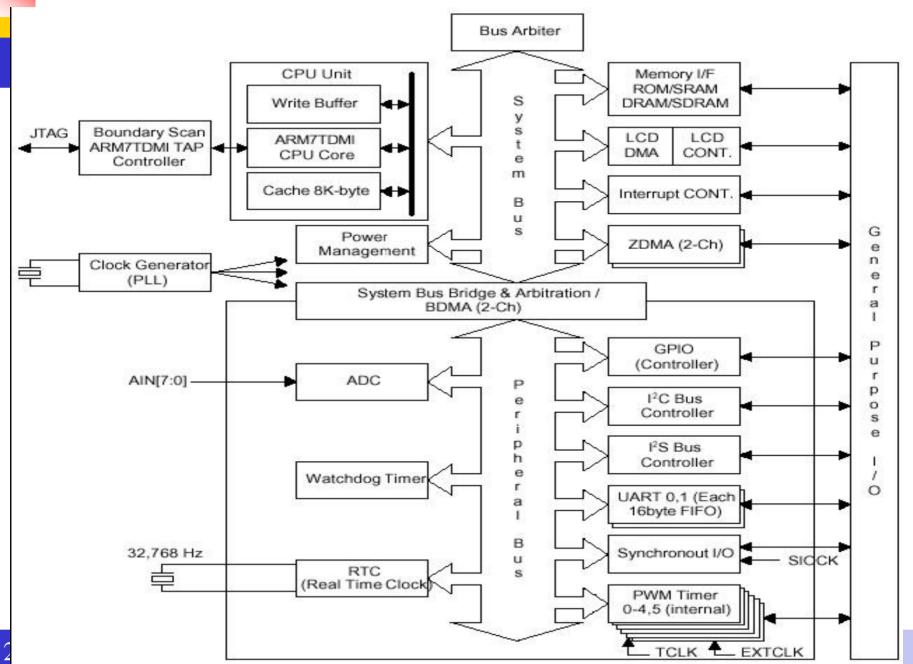

### ■ 概述

- S3C44BOX是 SAMSUNG公司推出的16/32位RISC处理器就,为手持设备和一般应用提供了高性价比和高性能的微控制器解决方案。

- S3C44B0X是使用ARM7TDMI内核,采用0.25μmCMOS工艺制造。它的低功耗和全静态设计特别适用于对成本和功耗敏感的应用。

- S3C44B0X的杰出特性是它的CPU核,是由ARM公司设计的16/32位ARM7TDMI RISC处理器(66MHz)。它包括了Thumb代码压缩器,一个片上的ICE断点调试支持和一个32位的硬件乘法器。

- S3C44BOX的特性 ------ 体系结构

- ① 16/32位RISC体系结构和ARM7TDMI处理器内核强大的指令体系;

- ② Thumb代码压缩机,最大化代码密度同时保持了 32位指令的性能;

- ③ 基于JTAG的片上集成ICE调方式支持解决方案;

- 4 32×8位硬件乘法器;

- ⑤ 实现低功耗SAMBAII的新型总线结构。

■ S3C44BOX的特性

S3C44BOX的体系

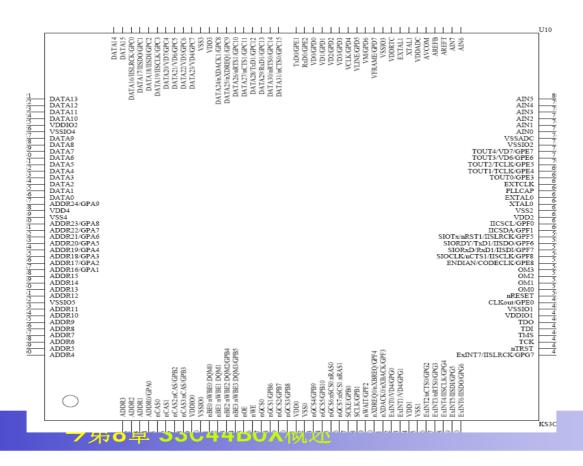

S3C44BOX的引脚 ----- 外形

■ S3C44BOX的引脚

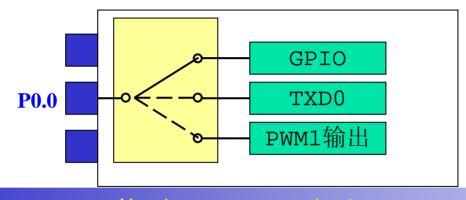

### -----引脚功能选择使用示例

S3C44BOX系列微控制器的引脚一般是多个功能复用,但是同一引脚在同一 引脚在同一时刻只能使用其中一个功能,这可以通过设置PINSELx寄存器来选择。

# 第8章 目录

- □1.S3C44B0简介

- □2.存储器管理

- □3.时钟和功耗管理

- □4.CUP Wrapper和总线 特性

- S3C44BOX存储系统的特点

- ① 有大端模式和小端模式。

- ② 地址空间具有8个存储体,每个存储体可达32MB,总共可达到256MB;

- ③ 对所有存储体的访问大小均可进行改变(8位/16位/32位),总线宽度可编程;

- ④ 8个存储体中,Bank0~Bank5可支持ROM、SRAM; Bank6、Bank7可支持ROM、SRAM和FP/EDO/SDRAM等,Bank6和Bank7存贮容量大小相同;

- 5 7个存储器的起始地址固定,1个存储器的起始地址可变。(即第8个可变)

### 系统的存储空间分配

- Bank 0: 两片 512 KF 1 a s h, 放置系统引导程序,系统 上电复位后,PC指针自动指向Bank 0 的第一个单 元,进行系统自举。。

- Bank1: K9F2808 (三星 16Mbyte Flash), 非线性 寻址。具体的时序可以参考K9F2808的datasheet

- Bank2: USBN9603。USB设备端接口芯片,占用系统外部中断0。8位数据总线。

- Bank3、Bank4未接设备。可以供扩展使用

- Bank5: RTL8019AS, ISA总线兼容的10M以太网 (PHY+MAC层)控制芯片。占用系统外部中断1, 16位数据总线

- Bank6: SDRAM, 起始地址为0xC000000。在SDRAM中, 前512Kbyte的空间划分出来,作为系统的LCD显示缓冲区使用(更新其中的数据,就可以更新LCD的显示)。系统的程序存储空间从0xC080000开始。也就是,引导系统的时候,需要把system.bin文件复制到0xC080000开始的地址空间,把PC指针指向0xC080000。

- Bank7: 未使用。可以扩展另一片SDRAM,或者其他的 外设。

- 系统的同步串行口(SIO),连接着触摸屏控制芯片 FM7843(与ADS7843完全兼容)。在同步串行口上,还 可以扩展其他的芯片。靠IO口控制设备的片选信号 (CS)来防止设备的冲突。

- 注: 系统的扩展接口上, A0的标号, 连接在S3C44B0X 的ADDR1上, 后面的地址依次向后错位。

S3C44BOX存储系统 的特点

------Bank6/Bank7存储器的地 址表

| 存储器   | 地址   | 2MB       | 4MB       | 8MB       | 16MB       | 32MB       |

|-------|------|-----------|-----------|-----------|------------|------------|

| Bank6 | 起始地址 | 0xc000000 | 0xc000000 | 0xc000000 | 0xc000000  | 0xc000000  |

|       | 结束地址 | Oxclfffff | 0xc3fffff | 0xc7fffff | Oxcffffff  | Oxcdffffff |

|       | 起始地址 | 0xc200000 | 0xc400000 | 0xc800000 | 0xc000000  | 0xe000000  |

| Bank7 | 结束地址 | 0xc3fffff | 0xc7fffff | Oxcffffff | Oxcdffffff | Oxcffffff  |

■ S3C44BOX存储系统 ---------- 存储器的大小端模式 的特点

当ENDIAN为L时则使用大端模式,大I小端模式 之所以存在是因为当在存储器中存储不同字长的数据 时,大I小端模式定义了不同长度的数据类型的对齐方 式。

■ S3C44BOX存储系统 -----总线宽度 的特点

因为Bank0是系统自举ROM存储体,所以必须在访问ROM之前定义Bank0的总线宽度

| OM1 | OM0 | 启动ROM的数据宽度/位 |

|-----|-----|--------------|

| 0   | 0   | 8            |

| 0   | 1   | 16           |

| 1   | 0   | 22           |

其他存储体的总线宽度只能在系统复位后由程序进行设定,由地址为0x01c8000的特殊寄存器BWSCON的相应位决定。

■ S3C44BOX存储系统 ---------- 存储器引脚连接的特点

| 存储地址引脚 | 8位数据总线下的<br>S3C44B0X地址                  | 16位数据总线下的<br>S3C44B0X地址 | 32位数据总线下的<br>S3C44B0X地址 |

|--------|-----------------------------------------|-------------------------|-------------------------|

| A0     | A0                                      | A1                      | A2                      |

| A1     | A1                                      | A2                      | A3                      |

| A2     | A2                                      | A3                      | A4                      |

| A3     | A3                                      | A4                      | A5                      |

| •      | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! |                         |                         |

■ S3C44BOX存储系统 --------- 存储器的分配的特点

| 存储器   | 与存储器接口            | 存储器   | 与存储器接口    |

|-------|-------------------|-------|-----------|

| Bank0 | BIOS 512KB×2Flash | Bank4 | 保留        |

| Bank1 | 16MB Flash硬盘      | Bank5 | 保留        |

| Bank2 | USB接口             | Bank6 | 系统内存SDRAM |

| Bank3 | LCD显示模块           | Bank7 | 保留        |

■ 寄存器定义

------BANKCONn控制寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应 着Bank—BANCONn寄存器针对操作时序进行设置,

| BANKC<br>ONn | Tacs    | Tcos    | Tacc   | Toch  | Tcah  | Трас  | PMC   |

|--------------|---------|---------|--------|-------|-------|-------|-------|

| 位            | [14:13] | [12:11] | [10:8] | [7:6] | [5:4] | [3:2] | [1:0] |

页模式存取周期

00=2时钟周期 01=3时钟周期

10=4时钟周期 11=6时钟周期 初值: 00

■ 寄存器定义

------BANKCONn控制寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应 着Bank—BANCONn寄存器针对操作时序进行设置,

| BANKC<br>ONn | Tacs    | Tcos    | Tacc   | Toch  | Tcah  | Tpac  | PMC   |

|--------------|---------|---------|--------|-------|-------|-------|-------|

| 位            | [14:13] | [12:11] | [10:8] | [7:6] | [5:4] | [3:2] | [1:0] |

页模式配置

00=正常

01=4时钟周期 10=8时钟周期 11=16时钟周期 初值?: 00

■ 寄存器定义

------BANKCONn控制寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应着Bank—BANCONn寄存器针对操作时序进行设置,

| BANKC<br>ONn | MT          | Tacs    | Tcos    | Tacc   | Toch  | Tcah  | Трас  | PMC   |

|--------------|-------------|---------|---------|--------|-------|-------|-------|-------|

| 位            | [16:<br>15] | [14:13] | [12:11] | [10:8] | [7:6] | [5:4] | [3:2] | [1:0] |

这两位决定了Bank6和Bank7的存储器类型 00=ROM or SRAM 01=FP DPAM 10=EDO DRAM 11=Sync,DRAM 初值: 11

■ 寄存器定义

-----REFRESH刷新寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应着Bank—BANCONn寄存器针对操作时序进行设置,

| REFRES<br>H | REFEN | TREFMD | Trp     | Trc     | Tchr    | Reserve<br>d | Refresh<br>Counter |

|-------------|-------|--------|---------|---------|---------|--------------|--------------------|

| 位           | [23]  | [22]   | [21:20] | [19:18] | [17:16] | [15:11]      | [10:0]             |

■ 寄存器定义

-----REFRESH刷新寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应着Bank—BANCONn寄存器针对操作时序进行设置,

| REFRES<br>H | REFEN | TREFMD | Trp     | Trc     | Tchr    | Reserve<br>d | Refresh<br>Counter |

|-------------|-------|--------|---------|---------|---------|--------------|--------------------|

| 位           | [23]  | [22]   | [21:20] | [19:18] | [17:16] | [15:11]      | [10:0]             |

#### DRAM/SDRAM刷新使新

**0**=禁止 **1**=允许(自动刷新) 初值:**1**

■ 寄存器定义

-----REFRESH刷新寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应着Bank—BANCONn寄存器针对操作时序进行设置,

| REFRES<br>H | REFEN | TREFMD | Trp     | Trc     | Tchr    | Reserve<br>d | Refresh<br>Counter |

|-------------|-------|--------|---------|---------|---------|--------------|--------------------|

| 位           | [23]  | [22]   | [21:20] | [19:18] | [17:16] | [15:11]      | [10:0]             |

DRAM/SDRAM刷新模式0=CBR/Auto刷新 1=自刷新,在self-refresh时,DRAM/SDRAM控制信号被适当电平驱动 初值: 0

■ 寄存器定义

-----REFRESH刷新寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应着Bank—BANCONn寄存器针对操作时序进行设置,

| REFRES<br>H | REFEN | TREFMD | Trp     | Trc     | Tchr    | Reserve<br>d | Refresh<br>Counter |

|-------------|-------|--------|---------|---------|---------|--------------|--------------------|

| 位           | [23]  | [22]   | [21:20] | [19:18] | [17:16] | [15:11]      | [10:0]             |

DRAI... -- ......... RAS 预充电时间

DRAM: 00=1.5时钟周期 01=2.5时钟周期

10=3.5时钟周期 11=4.5时钟周期

SDRAM: 00=2时钟周期 01=3时钟周期

10=4时钟周期 11=无 初值: 10

■ 寄存器定义

-----REFRESH刷新寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应着Bank—BANCONn寄存器针对操作时序进行设置,

| REFRES<br>H | REFEN | TREFMD | Trp     | Trc     | Tchr    | Reserve<br>d | Refresh<br>Counter |

|-------------|-------|--------|---------|---------|---------|--------------|--------------------|

| 位           | [23]  | [22]   | [21:20] | [19:18] | [17:16] | [15:11]      | [10:0]             |

#### SDRAM RC最小时间:

00=4时钟周期 01=5时钟周期

10=6时钟周期 11=7时钟周期 初值: 11

■ 寄存器定义

-----REFRESH刷新寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应 着Bank—BANCONn寄存器针对操作时序进行设置,

| REFRES<br>H | REFEN | TREFMD | Trp     | Trc     | Tchr    | Reserve<br>d | Refresh<br>Counter |

|-------------|-------|--------|---------|---------|---------|--------------|--------------------|

| 位           | [23]  | [22]   | [21:20] | [19:18] | [17:16] | [15:11]      | [10:0]             |

CAS保持时间 (DRAM)

00=1时钟周期 01=2时钟周期

10=3时钟周期 11=4时钟周期 初值: 00

■ 寄存器定义

-----REFRESH刷新寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应着Bank—BANCONn寄存器针对操作时序进行设置,

| REFRES<br>H | REFEN | TREFMD | Trp     | Trc     | Tchr    | Reserve<br>d | Refresh<br>Counter |

|-------------|-------|--------|---------|---------|---------|--------------|--------------------|

| 位           | [23]  | [22]   | [21:20] | [19:18] | [17:16] | [15:11]      | [10:0]             |

未用 初值: 0000

■ 寄存器定义

-----REFRESH刷新寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应着Bank—BANCONn寄存器针对操作时序进行设置,

| REFRES<br>H | REFEN | TREFMD | Trp     | Trc     | Tchr    | Reserve<br>d | Refresh<br>Counter |

|-------------|-------|--------|---------|---------|---------|--------------|--------------------|

| 位           | [23]  | [22]   | [21:20] | [19:18] | [17:16] | [15:11]      | [10:0]             |

DRAM/SDRAM刷新计数值 初值: 0

■ 寄存器定义

------ BANKSIAE寄存器

### BANKSIAE寄存器定义了Bank的大小

| BANDSIZE | SCLKEN | Reserved | BK76MAP |

|----------|--------|----------|---------|

| 位        | 4      | 3        | 2:0     |

■ 寄存器定义

------ BANKSIAE寄存器

### BANKSIAE寄存器定义了Bank的大小

| BANDSIZE | SCLKEN | Reserved | BK76MAP |

|----------|--------|----------|---------|

| 位        | 4      | 3        | 2:0     |

设置为1,则SCLK 仅在SDRAM存取周期产生,这个特征将使功能减少,推荐设置为1,0=标准1=低功能

■ 寄存器定义

------ BANKSIAE寄存器

### BANKSIAE寄存器定义了Bank的大小

| BANDSIZE | SCLKEN | Reserved | BK76MAP |

|----------|--------|----------|---------|

| 位        | 4      | 3        | 2:0     |

无

■ 寄存器定义

------ BANKSIAE寄存器

### BANKSIAE寄存器定义了Bank的大小

| BANDSIZE | SCLKEN | Reserved | BK76MAP |

|----------|--------|----------|---------|

| 位        | 4      | 3        | 2:0     |

Bank6/Bank7存储映射

000: 32MB/32MB 100: 2MB/2MB 101: 4MB/4MB

110: SMB/SMB 111: 16MB/16MB

■ 寄存器定义

------ MRSR寄存器

### MRSR是SDRAM模式设置寄存器

| MRSR | Reserved | WBL | TM    | CL    | ВТ  | BL    |

|------|----------|-----|-------|-------|-----|-------|

| 位    | [11:10]  | [9] | [8:7] | [6:4] | [3] | [2:0] |

■ 寄存器定义

----- MRSR寄存器

### MRSR是SDRAM模式设置寄存器

| MRSR | Reserved | WBL | TM    | CL    | ВТ  | BL    |

|------|----------|-----|-------|-------|-----|-------|

| 位    | [11:10]  | [9] | [8:7] | [6:4] | [3] | [2:0] |

无

■ 寄存器定义

------ MRSR寄存器

## MRSR是SDRAM模式设置寄存器

| MRSR | Reserved | WBL | TM    | CL    | ВТ  | BL    |

|------|----------|-----|-------|-------|-----|-------|

| 位    | [11:10]  | [9] | [8:7] | [6:4] | [3] | [2:0] |

写突发脉冲长度 推荐值为0

■ 寄存器定义

------ MRSR寄存器

## MRSR是SDRAM模式设置寄存器

| MRSR | Reserved | WBL | TM    | CL    | BT  | BL    |

|------|----------|-----|-------|-------|-----|-------|

| 位    | [11:10]  | [9] | [8:7] | [6:4] | [3] | [2:0] |

测试模式

00: 设置寄存器模式 01,10,11: 保留

■ 寄存器定义

----- MRSR寄存器

## MRSR是SDRAM模式设置寄存器

| MRSR | Reserved | WBL | TM    | CL    | ВТ  | BL    |

|------|----------|-----|-------|-------|-----|-------|

| 位    | [11:10]  | [9] | [8:7] | [6:4] | [3] | [2:0] |

CAS突发响应时间 000=1时钟周期 010=2时钟周期 011=3时钟周期 其他保留

■ 寄存器定义

------ MRSR寄存器

## MRSR是SDRAM模式设置寄存器

| MRSR | Reserved | WBL | TM    | CL    | ВТ  | BL    |

|------|----------|-----|-------|-------|-----|-------|

| 位    | [11:10]  | [9] | [8:7] | [6:4] | [3] | [2:0] |

突发类型

0: 连续的(推荐)

1: 不适用

■ 寄存器定义

----- MRSR寄存器

## MRSR是SDRAM模式设置寄存器

| MRSR | Reserved | WBL | TM    | CL    | ВТ  | BL    |

|------|----------|-----|-------|-------|-----|-------|

| 位    | [11:10]  | [9] | [8:7] | [6:4] | [3] | [2:0] |

突发长度

000: 1

其他不适用

## 第8章 目录

- □1.S3C44B0简介

- □2.存储器配置

- □3.时钟和功耗管理

- ■4.CUP Wrapper和总线 特性

■ 概述

S3C44B0X的时钟产生器可以为CPU产生要求的时钟信号,同样也为外设提供了时钟信号。时钟产生器可以通过软件来控制是否为每个外部设备模块提供时钟信号,或者切断与外部设备的联系,以减少功耗。

概述

## S3C44B0X 中的功耗管理提供5种模式

■ 寄存器定义 -----PLL控制寄存器

### PLL控制寄存器设置PLL参数

PLL输出频率计算公式如下:

Fpllo = (m \* Fin)/(p \* 2s)

其中m = (MDIV + 8),p = (PDIV + 2),s = SDIV,

Fpllo必须大于20MHZ且少于66MHZ,

Fpllo \* 2s必须少于170MHZ,

Fin/p推荐为1MHZ或大于,但小于2MHZ

|     | PLLCON | 位       | 描述   | 初始状态 |

|-----|--------|---------|------|------|

| -   | MDIV   | [19.12] | 主分频值 | 0x38 |

| .0/ | PDIV   | [9:4]   | 预分频值 | 0x08 |

| 0   | SDIV   | [1:0]   | 后分频值 | 0x0  |

200

■ 寄存器定义

| CL<br>KC<br>ON | IIS | IIC | AD<br>C | RT<br>C | GPI<br>O | UA<br>RT<br>1 | RA<br>RT<br>0 | BD<br>MA<br>0,1 |   | SIO | ZD<br>MA<br>0,1 | PW<br>MT<br>IM<br>ER | IDL<br>E | SL_<br>IDL<br>E | ST<br>OP |

|----------------|-----|-----|---------|---------|----------|---------------|---------------|-----------------|---|-----|-----------------|----------------------|----------|-----------------|----------|

| 15             | 14  | 13  | 12      | 11      | 10       | 9             | 8             | 7               | 6 | 5   | 4               | 3                    | 2        | 1               | 0        |

■ 寄存器定义

| CL<br>KC<br>ON | IIS | IIC | AD<br>C | RT<br>C | GPI<br>O | UA<br>RT<br>1 | RA<br>RT<br>0 | BD<br>MA<br>0,1 | LC<br>DC | SIO | ZD<br>MA<br>0,1 | PW<br>MT<br>IM<br>ER | IDL<br>E | SL_<br>IDL<br>E | ST<br>OP |

|----------------|-----|-----|---------|---------|----------|---------------|---------------|-----------------|----------|-----|-----------------|----------------------|----------|-----------------|----------|

| 15             | 14  | 13  | 12      | 11      | 10       | 9             | 8             | 7               | 6        | 5   | 4               | 3                    | 2        | 1               | 0        |

控制RTC block的钟控,即使该位为0,RTC定时器仍工作。0=禁止 1=允许

■ 寄存器定义 ------ 时钟控制寄存器

| CL<br>KC<br>ON | IIS | IIC | AD<br>C | RT<br>C | GPI<br>O | UA<br>RT<br>1 | RA<br>RT<br>0 | BD<br>MA<br>0,1 | LC<br>DC | SIO | ZD<br>MA<br>0,1 | PW<br>MT<br>IM<br>ER | IDL<br>E | SL_<br>IDL<br>E | ST<br>OP |

|----------------|-----|-----|---------|---------|----------|---------------|---------------|-----------------|----------|-----|-----------------|----------------------|----------|-----------------|----------|

| 15             | 14  | 13  | 12      | 11      | 10       | 9             | 8             | 7               | 6        | 5   | 4               | 3                    | 2        | 1               | 0        |

控制BDMA block的钟控,如果BDMA关断,在外设总线上的外设不能存取。 0=禁止 1=允许

■ 寄存器定义 -----慢射钟控制寄存 器

| CLKSLOW | PLL_OFF | SLOW_BIT | SLOW_VA<br>L |

|---------|---------|----------|--------------|

| 位       | [5]     | [4]      | [3:0]        |

■ 寄存器定义 -----慢肘钟控制寄存 器

| CLKSLOW | PLL_OFF | SLOW_BIT | SLOW_VA<br>L |

|---------|---------|----------|--------------|

| 位       | [5]     | [4]      | [3:0]        |

0:PLL打开,PLL仅能在SLOW-BIT=1时打开,在PLL稳定后(150us),

SLOW—BIT位可以清除1: PLL-BIT关掉, PLL仅能在SLOW-BIT=1时关掉

■ 寄存器定义 -----慢肘钟控制寄存器

| CLKSLOW | PLL_OFF | SLOW_BIT | SLOW_VA<br>L |

|---------|---------|----------|--------------|

| 位       | [5]     | Γ41      | [3:0]        |

0:Fout=Fpllo(PLL output)

1:Fout=Fin/(2\*SLOW-VAL),(SLOW-VAL>0)

Fout=Fin,(SLOW-VAL=0)100

■ 寄存器定义 -----慢射钟控制寄存 器

| CLKSLOW | PLL_OFF | SLOW_BIT | SLOW_VA |

|---------|---------|----------|---------|

| 位       | [5]     | [4]      | [3:0]   |

这四位是在SLOW-BIT位打开时slow clock的分频值

■ 寄存器定义 ------锁定时间计数值寄存器

| LOCKTIME     | 位      | 描述             | 初始值   |

|--------------|--------|----------------|-------|

| LTIME<br>CNT | [11:0] | PLL锁定时间计数<br>值 | oxfff |

## 第8章 目录

- □1.S3C44B0简介

- □2.存储器配置

- □3.时钟和功耗管理

- ■4.CUP Wrapper和总线 特性

■ 概述

处理器 wrapper 包括一个cache、写入缓冲器和 CPU内核。总线仲裁逻辑决定每个总线占用者的优先 权。

## 内部SRAM

S3C44B0X 具有一个最小 8KB 的 4 组相连 cache 或内部 SRAM。

如果内部 SRAM 为 4KB, 另外 4KB 内部存储器可以用来作为 2 组相连 cache。

内部 SRAM 的存储器操作周期为 1MCLK。

■ 总线优先级

在 S3C44B0X 中,有 7 种总线 控 刷新控制器 制器:

LCD\_DMA;BDMA0;BDMA1;

ZDMA0;ZDMA1;Nbreq(外部总线)

master); CPU wrapper。

LCD\_DMA

**DMA**

ZDMA0,1

BDMA0,1

外部总线控制器

写缓冲区

2007-10-22

→第8章 S3

Cache 和CPU

■ 写缓冲区操作

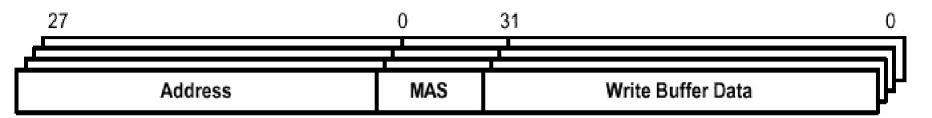

S3C44B0X 有 4 个写缓冲区寄存器来提高存储器的写性能。每个寄存器包括一个 32 位数据区域, 28 位的地址区域和 2 位的状态区域。

■ 写缓冲区操作

[31:0] Write Buffer Data 将要写到外部存储器中的数据

#### [1:0] MAS

00 = 8-bit 数据模式

01 = 16-bit 数据模式

10 = 32-bit 数据模式

11 = Not used

[27:0] Address 写入数据的地址

■ 寄存器定义

----- SYSCFG寄存器

| SYSCFG | Reserved | Reserved | DA(reser ved) | RSE (reserve d) | WE  | CM    | SE  |

|--------|----------|----------|---------------|-----------------|-----|-------|-----|

| 位      | [7]      | [6]      | [5]           | [4]             | [3] | [2:1] | [0] |

■ 寄存器定义

----- SYSCFG寄存器

| SYSCFG | Reserved | Reserved | DA(reser ved) | RSE (reserve d) | WE  | CM    | SE  |

|--------|----------|----------|---------------|-----------------|-----|-------|-----|

| 位      | [7]      | [6]      | [5]           | [4]             | [3] | [2:1] | [0] |

保留

■ 寄存器定义

----- SYSCFG寄存器

| SYSCFG | Reserved | Reserved | DA(reser ved) | RSE (reserve d) | WE  | CM    | SE  |

|--------|----------|----------|---------------|-----------------|-----|-------|-----|

| 位      | [7]      | [6]      | [5]           | [4]             | [3] | [2:1] | [0] |

保留

■ 寄存器定义

----- SYSCFG寄存器

| SYSCFG | Reserved | Reserved | DA(reser ved) | RSE (reserve d) | WE  | СМ    | SE  |

|--------|----------|----------|---------------|-----------------|-----|-------|-----|

| 位      | [7]      | [6]      | <b>[5]</b>    | [4]             | [3] | [2:1] | [0] |

数据异常控制,推荐值为0。

0: 允许数据异常1: 不允许数据异常

初值 0

■ 寄存器定义

----- SYSCFG寄存器

| SYSCFG | Reserved | Reserved | DA(reser ved) | RSE (reserve d) | WE  | CM    | SE  |

|--------|----------|----------|---------------|-----------------|-----|-------|-----|

| 位      | [7]      | [6]      | [5]           | Γ41             | [3] | [2:1] | [0] |

允许读停止选项,推荐值为0。

读停止选项在Cache & CPU core读数据时插入—个间歇等待周期。

0: 允许读停止 1: 允许读停止 初值 0

■ 寄存器定义

----- SYSCFG寄存器

| SYSCFG | Reserved | Reserved | DA(reser ved) | RSE (reserve d) | WE  | CM    | SE  |

|--------|----------|----------|---------------|-----------------|-----|-------|-----|

| 位      | [7]      | [6]      | [5]           | [4]             | Г31 | [2:1] | [0] |

该位确定写缓冲的允许/不允许,一些外部装置需要最小的写周期时间, 如果允许写缓冲,在由于连续的写之间的周期将使之工作不正常。

0=不允许写缓冲操作 1=允许写缓冲操作

■ 寄存器定义

----- SYSCFG寄存器

| SYSCFG | Reserved | Reserved | DA(reser ved) | RSE (reserve d) | WE  | СМ    | SE  |

|--------|----------|----------|---------------|-----------------|-----|-------|-----|

| 位      | [7]      | [6]      | [5]           | [4]             | [3] | Γ2:11 | [0] |

这两位确定Cache模式 00=8KB内部SRAM 01=4KB Cache ,4KB 内部SRAM

10=保留 11=8KB Cache 初值 00

■ 寄存器定义

----- SYSCFG寄存器

| SYSCFG | Reserved | Reserved | DA(reser ved) | RSE (reserve d) | WE  | СМ    | SE  |

|--------|----------|----------|---------------|-----------------|-----|-------|-----|

| 位      | [7]      | [6]      | [5]           | [4]             | [3] | [2:1] | [0] |

允许停止选项,推荐值为0。

停止选项在使用Cache,产生非连续地址时,插入—

0: 不允许停止 1: 允许停止 初值 1

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

优先模式

0: 轮转优先级 1: 固定优先级

初值 0xl

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

指示LCD\_DMA的总线优先级(只读)

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

指示ZDMA的总线优先级(只读)

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

指示BDMA的总线优先级(只读)

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

指示nBREQQ的总线优先级(只读)

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

指示LCD\_DMA的总线优先级

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

指示ZDMA的总线优先级

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

指示BDMA的总线优先级

■ 寄存器定义

----- SBUSCON寄存

器

| SBUSC<br>ON | FIX  | S_LCD<br>_DMA | S_ZD<br>MA | S_BD<br>MA | S_nBR<br>EQ | LCD_<br>DMA | ZDMA  | BDMA  | nBREQ |

|-------------|------|---------------|------------|------------|-------------|-------------|-------|-------|-------|

| 位           | [31] | [15:14]       | [13:12]    | [11:10     | [9:8]       | [7:6]       | [5:4] | [3:2] | [1:0] |

指示nBREQ的总线优先级

# 讲讲